|

2.2 Altera APEX 20K 系列器件

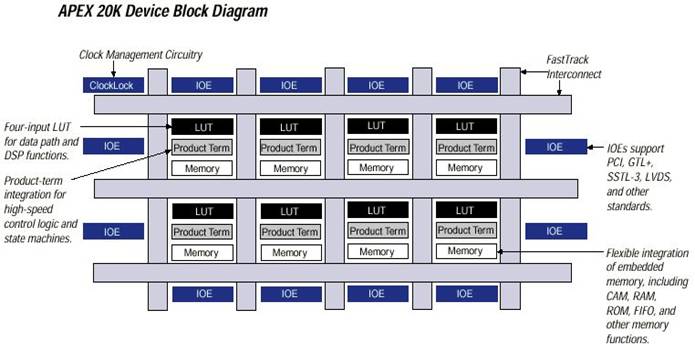

一. 性能特点 (1)工业界第一种实现可编程片上系统(System On a Programmable Chip_SOPC)的PLD 多核结构:查找表(LUT)逻辑、乘积项逻辑、嵌入式系统块(ESB_Embedded System Block) (2)高密度: 100000 to 1.5 million门/片,540,672位 RAM。 (3)系统级特点 -- 低功率模式设计:1.8V、2.5V电源电压。 -- 内建 4个PLL、灵活的时钟管理电路。 时钟锁定(Clock Lock)电路; 时钟自举(Clock Boost)电路; 时钟相移(Clock Shift)电路; -- 功能强大的多电压 I/O接口标准。 兼容PCI接口; 支持:1.8V,2.5V,3.3V器件; -- JTAG(Joint Test Action Group)。 (4)先进的内部连接结构 -- 四层快速通道(Fast Track)连续式 布线结构,延迟可预测 -- 专用进位链 -- 专用级联链 (5)丰富的封装形式和器件类型 144 -1020 个引脚 (6)先进的软件支持 Altera Quartus 开发系统支持 多种工作平台上:

二. 功能描述 查找表(LUT)、乘积项、嵌入式系统块(ESB)、连续式Fast Track和 I/O 单元

我们可以从嵌入式系统块 ESB、MegaLAB结构及逻辑单元、Fast Track 互连结构、I/O单元、时钟管理电路对APEX20K进行描述。 1.APEX20K嵌入式系统块 ESB (Embedded System Block) 可用于实现:FIFO、ROM、RAM、CAM、乘法器、数字滤波器、微处理器、同步设计、异步设计

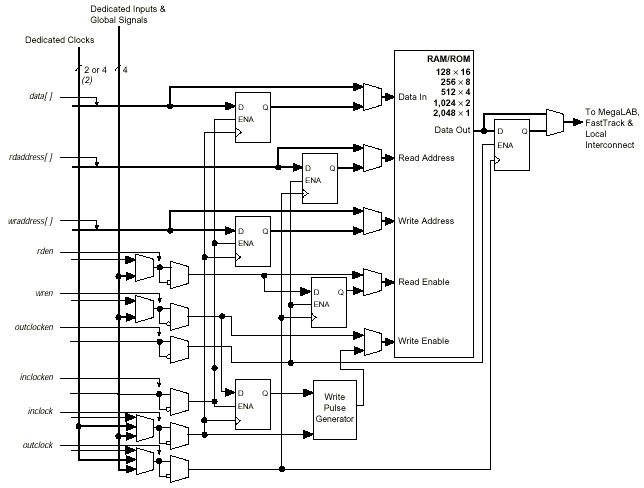

ESB 模块图

(2)、用 ESB实现 RAM功能,ESB中RAM的大小可灵活配置:

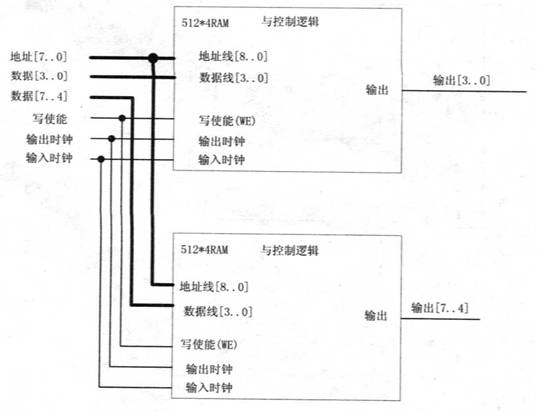

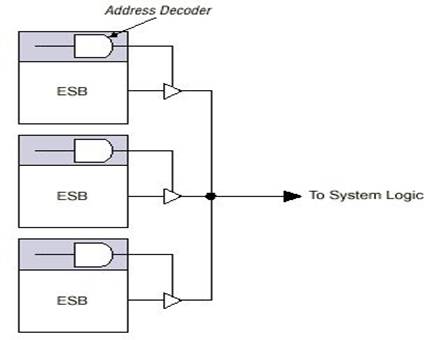

(a) 将ESB级联成“更宽”的RAM。开发软件自动级联(无需附加逻辑) APEX20K ESB与 FPGA中分布式RAM的区别: FPGA中:小型单个(16x1) RAM分布块组成大RAM时,存取时间变长,并占用大量器件资源。

扩展ESB

(b)将ESB扩展成“更深”的RAM 叁个2048x1 ESB自动复用成一个6144x1 ESB块:

复用ESB (c)实现同步RAM、异步RAM (d)仿真ROM (3)、用ESB 实现FIFO功能 (4)、用ESB实现CAM(Content-Addressable Memory) (5)、ESB构成查找表LUT(Look up Table) (6)、ESB与逻辑单元的比

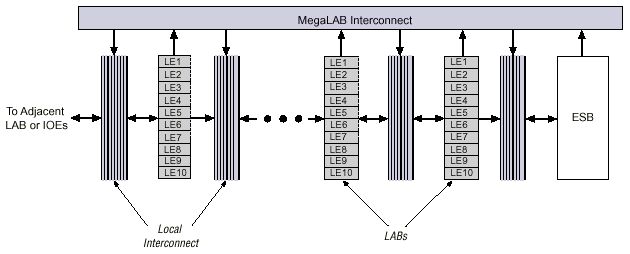

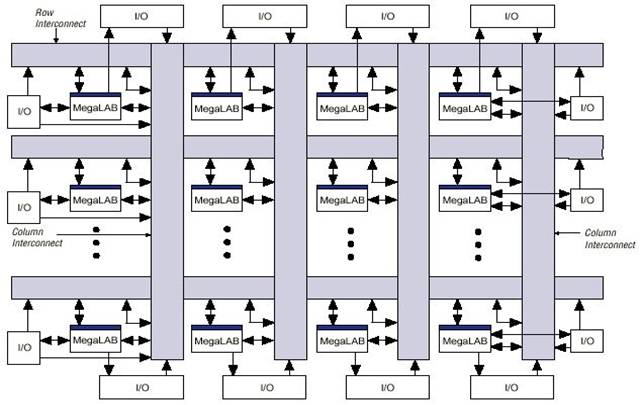

10个LE = 逻辑阵列块(LAB_Logic Array Block) 最小单元:LE(Logic Element) 16个LAB + ESB + 互连矩阵 = 一个MegaLAB

APEX 20K MegaLAB的方块图

(1)、逻辑阵列块(LAB) LAB包括10个LE、LAB控制信号及局部互连矩阵。

APEX 20K LAB的方块图

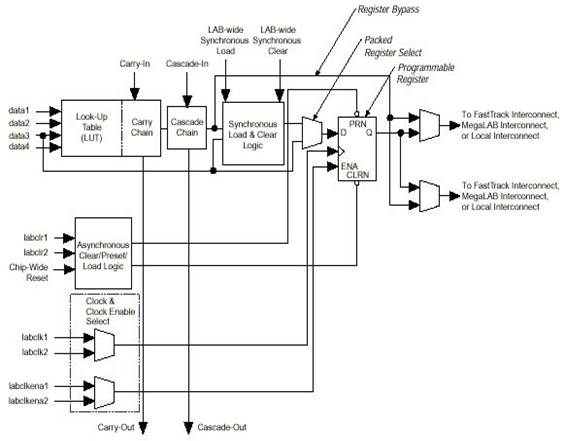

(2)、逻辑单元( LE ) 四个部分:(a)查找表(b)可编程寄存器

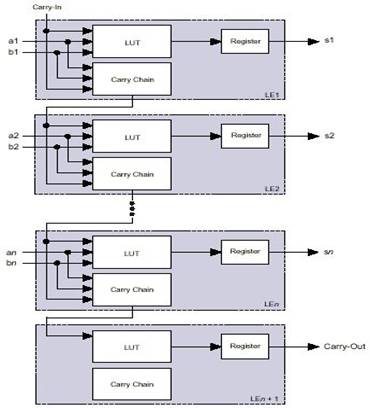

APEX 20K LE的方块图 (c)进位链:专用高速数据通道。LE之间约0.2ns 高速向前进位。 用于:高速计数器、任意位数加法器、比较器等。 n+1个LE实现n位全加器 LUT分成两部分:一部分产生两输入信号及进位信号的“和”;一部分产生进位输出信号。

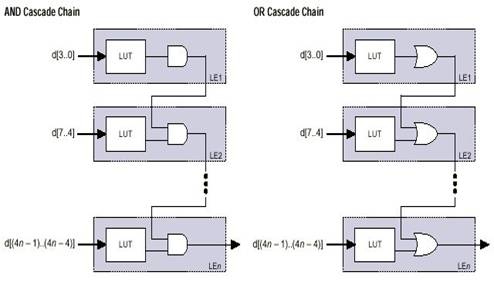

进位链操作 (c)级联链:专用高速数据通道。用相邻的多个 LUT 分别计算函数的各个部分,实现高扇入的逻辑函数。 n个LE实现4n个变量的函数

级联链操作

Fast Track组成:行连线带、列连线带 特点:快速并且布线延迟可预测

APEX 20K 器件的互连资源

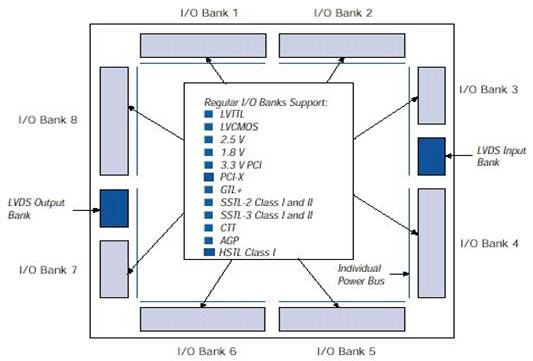

(1)、I/O Banks(APEX20KE)

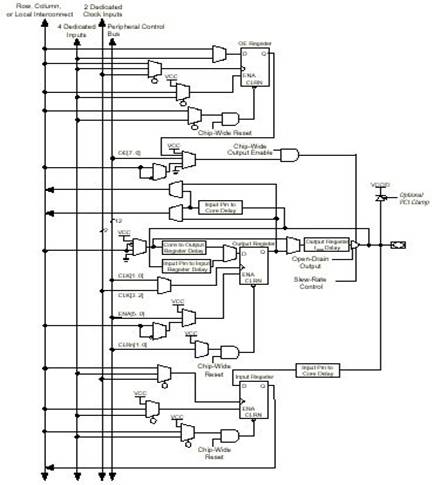

(2)、I/O单元 特点: 1、双向I/O 2、双向寄存器 3、电压摆率可调 4、集电极可开路 5、延迟可调

APEX20K器件I/O(IOE)

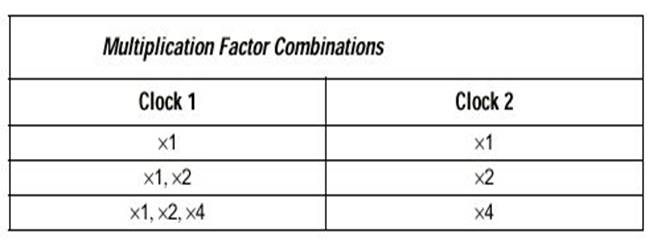

APEX 20K: Clock Lock、Clock Boost APEX 20KE:Clock Lock、Clock Boost 、Clock Shift

|

|||