|

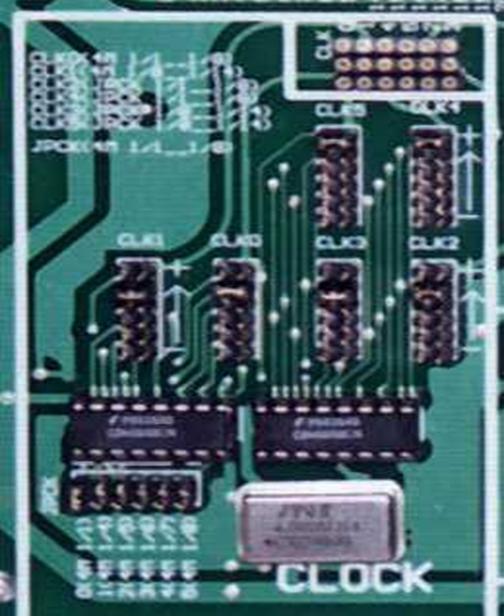

5. 实验系统箱介绍 (二)时钟源 六路单独时钟(4MHz ~ 1Hz),按频率范围高低排列为:CLK0>CLK1>CLK2= CLK4>CLK3 = CLK5 通过两组跳线排进行分频

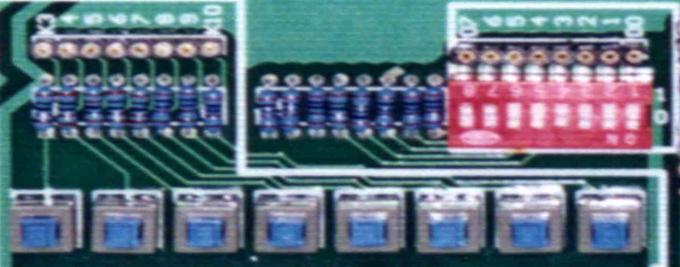

(三)普通输入输出器件接口 1、静态逻辑高、低电平的提供 主板中间偏上(主芯片接口板上方)的“Low”、“High”提供“0”、“1” 逻辑电平。 2、开关 主板中间偏下位置设有:8个按键开关K3 ~ K10(不按为“1”,按下 为“0”)一个8位拨码开关D7 ~ D0(拨上为“1”,拨下为“0”)

3、LED灯 主板中间偏上位置有成环形排列的12个LED灯:RED1 ~ 4, GRN1 ~ 4,YEL1 ~ 4,输入高电平亮。 主板右下有8个红色LED灯,LED8 ~ 1端,输入高电平亮。

|

|||