实验一:八位全加器的设计与仿真

一、要求

1、用VHDL设计一个四位并行全加器;

2、用图形方式构成一个八位全加器的顶层文件;

二、目的

1、掌握图形设计方法。

2、熟悉MAX+PLUSⅡ软件的使用及设计流程;

3、掌握全加器原理,能进行多位加法器的设计。三、实验原理与内容

1、原理:

加法器是数字系统中的基本逻辑器件。例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

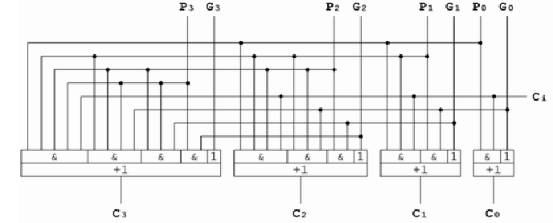

实验表明,4位二进制并行加法器和串行级联加法器占用几乎相同的资源。这样,多位数加法器由4位二进制并行加法器级联构成是较好的折中选择。因此本实验中的8位加法器采用两个4位二进制并行加法器级联而成。

2、实现框图:

1)、四位加法器

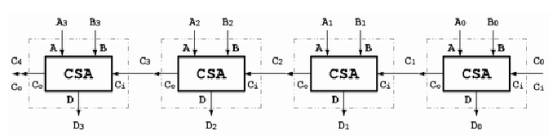

四位加法器可以采用四个一位全加器级连成串行进位加法器,实现框图如下图所示,其中CSA为一位全加器。显然,对于这种方式,因高位运算必须要等低位进位来到后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

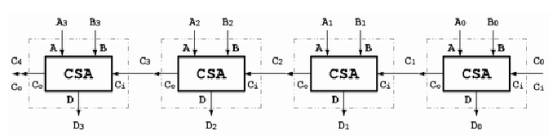

通过对串行进位加法器研究可得:运算的延迟是由于进位的延迟。基于此,减小进位的延迟对提高运算速度非常有效。下图是减少了进位延迟的一种实现方法。可见,将迭代关系去掉,则各位彼此独立,进位传播不复存在。因此,总的延迟是两级门的延迟,其高速也就自不待言。

2)、八位加法器

用两个并行四位加法器实现一个八位加法器的框图如下:

四、实验步骤

2、

利用步骤一得到的四位全加器使用图形输入法实现一个8位全加器;

3、

对最后的顶层文件进行编译、仿真和下载;

4、

如果时间有余可以直接设计一个八位的串行全加器,比较上述两种方法综合后的不同(主要从消耗资源和运算速度考虑)。

五、实验报告

1、写出实验源程序,并附上综合结果和仿真波形;

2、分析实验结果;

3、心得体会――本次实验中你的感受;你从实验中获得了哪些收益;本次实验你的成功之处;本次实验中还有待改进的地方;下次实验应该从哪些地方进行改进;怎样提高自的实验效率和实验水平等等。

4、完成实验思考题。

六、问题及思考

试设计由8

位二进制加法器为基本元件构成的8位减法器。

提示:根据二进制数相减等于补码相加的原理,将减数的每一位取反,同时将加法器的借位输入置为高电平(这种方法占用资源最少)。注意:这种结构的减法器,其溢出或借位的输出电平为0。