实验三:

1、具有清除端、使能端,计数范围为0--999的

计数器设计,输出为8421BCD码。

2、8421BCD码--七段LED译码显示电路设计。

一、要求

1、用VHDL设计上述两个电路。

2、完成时序仿真,验证所实现的功能。

二、目的

1、重点掌握VHDL设计电路模块的描述方法,

2、进一步学习开发系统,掌握MAX+PLUS II的设计流程。

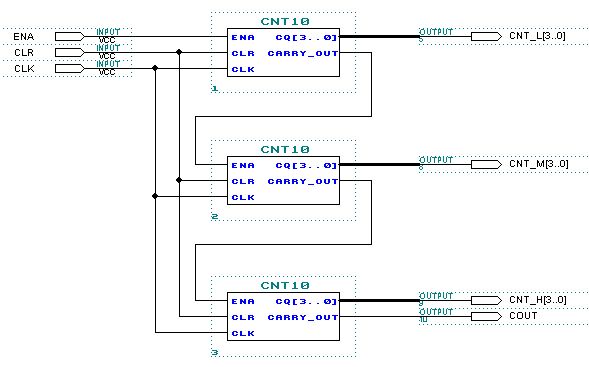

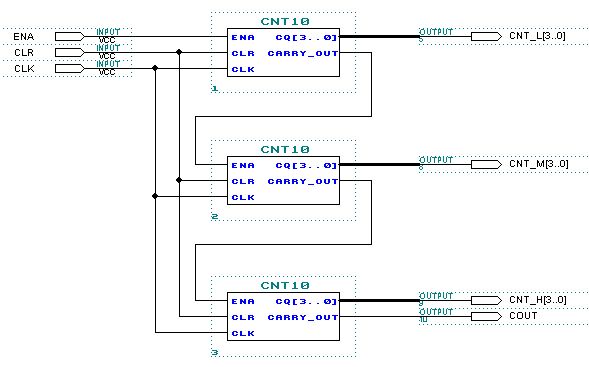

三、3位十进制计数器的原理图

四、扩展部分

3位十进制计数器的设计可如图所示:先采用VHDL语言设计1位十进制计

数器,然后根据模块化方式构成图示的3位十进制计数器。

3位十进制计数器也可直接由VHDL语言在一个实体内进行完整描述,则整

个设计更加简洁、效率更高。

比较两种设计方式的区别、各自的优缺点。