实验四:动态扫描显示电路设计与实现

一、要求

1、用VHDL语言设计显示信号选择及动态扫描控制电路。

2、完成电路设计的芯片下载工作。

3、将实验二中的3位计数器的输出值用数码管显示出来。

二、目的

1、继续学习VHDL语言设计电路模块。

2、了解实验系统箱中数码管显示模块的动态扫描工作原理,学习实验系

统箱的操作使用。

3、完成设计电路的硬件验证工作。

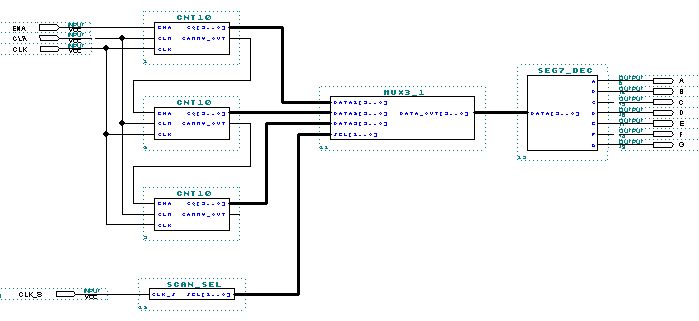

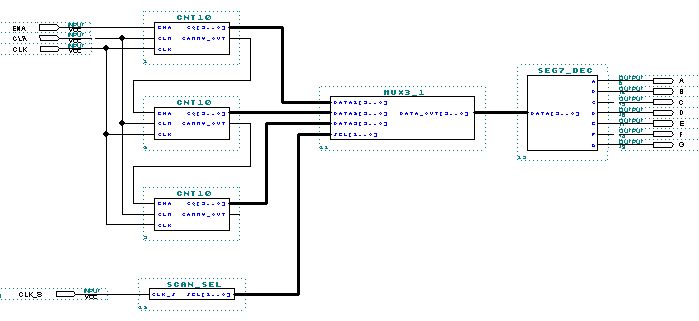

三、设计原理图

四、扫描原理说明

为了减少8位显示信号的接口连接线,实验箱中的数码显示采用扫描

显示工作模式。即8位数码管的七段译码输入(7seg[6..0])是并联在

一起的,而每一个数码管是通过一个3位选择信号(sel[2..0])来选定

的。sel与数码管之间是一3-8译码的关系,即sel为“000”时,选中第

一个数码管,sel为“001”时,选中第二个数码管,…,sel为“111”

时,选中第八个数码管。实验箱中已有该3-8译码电路,不用再设计。

为了正确显示信息,必须在某一时间段提供相应位的七段译码值

7seg 和对应位的选择控制信号sel,并使 7seg 和 sel 的值按一定频

率从最低位至最高位循环变化,即在第一时间段,输出第一位的7seg

的值,sel为“000”;第二时间段输出第二位的7seg的值,sel为“001”;

…;第八时间段输出第八位的7seg的值,sel为“111”;循环输出,则

可构成扫描显示。