实验五:数字频率计的设计及实现

一、要求

1、用VHDL完成 8位数字频率计的设计及时序仿真。

2、频率测量范围:0 -- 99999999 Hz 。

3、基准频率:20 MHz、10MHz、5MHz可选。

4、用实验系统箱实现该频率计,并用数码管显示所测的频率值。

5、对频率计的测量精度进行分析,完成实验总结报告,并提出改进设计方案。

二、目的

本实验是一综合的设计课题,是前面三次设计的一个总结和提高。培养学

生的系统设计思想和系统综合设计能力。通过一个实际系统的设计和实现,

提高学生的工程素养。

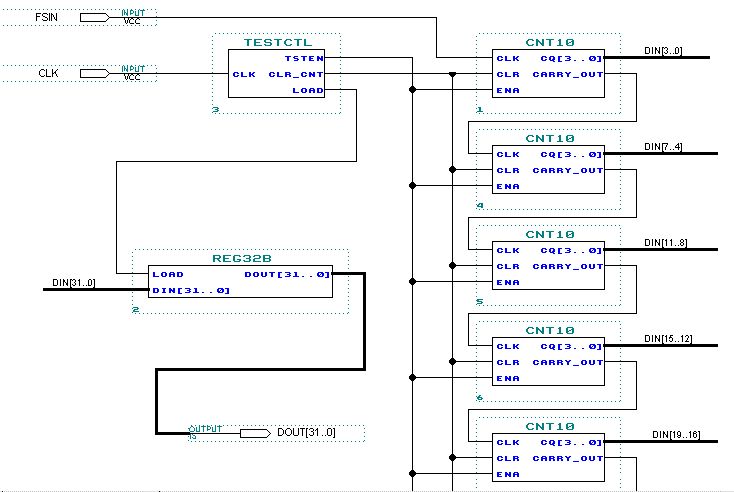

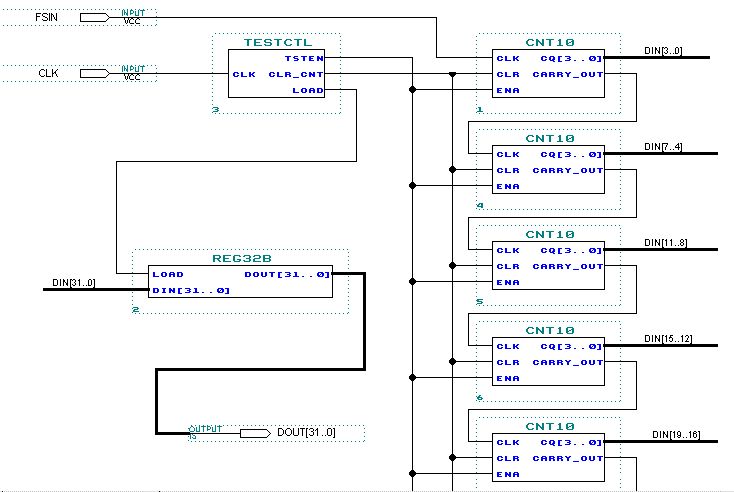

三、系统原理图(部分)

四、扩展部分

整个系统的描述可以采用不同的方式,以上原理图仅供参考。学生可根据题

意要求发挥能动性,自行进行整体设计,模块化分等,培养自已的创新能力。