实验三:八位乘法器的设计

一、要求

1、用VHDL设计一个八位乘法器;

2、完成时序仿真,验证所实现的功能。

二、目的

1、重点掌握VHDL设计电路模块的描述方法;

2、在掌握8位加法器设计的基础上,进一步掌握8×8位乘法器的设计;

3、进一步学习开发系统,掌握MAX+PLUS II的设计流程。

三、实验原理

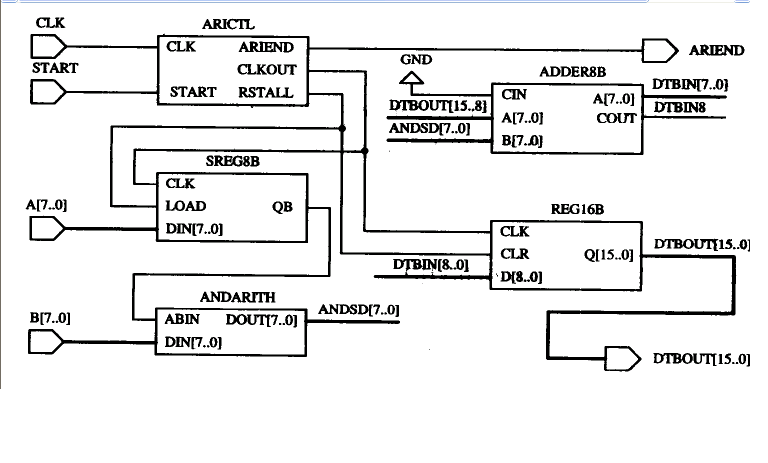

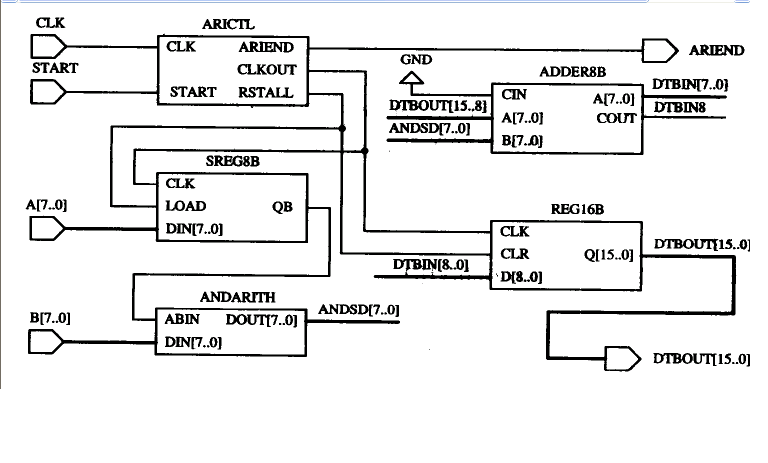

由8位加法器构成的以时序逻辑方式设计的8位乘法器,此乘法器具有一定的实用价值。其乘法原理是:乘法通过逐项位移相加原理来实现,从被乘数的最低位开始,若为1,则乘数左移后与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。

图中,ARICTL是乘法运算控制电路,它的START(可锁定于引脚I/O 49)信号的上跳沿与高电平有两个功能,即16位寄存器清零和被乘数A[7..0]向移位寄存器SREG8B加载:它的低电平则作为乘法使能信号。乘法时钟信号从ARICTL的CLK输入。当被乘数加载于8位右移寄存器SREG8B后,随着每一时钟节拍,最低位在前,由低位至高位逐位移出。当为1时,与门ANDARITH打开,8为乘数B[7..0]在同一节拍进入8位加法器,与上一次锁存在16位锁存器REG16B中的高8位进行相加,其和在下一时钟节拍的上升沿被锁进此锁存器。而当被乘数移出位为0时,与门全零输出。如此往复,直至8个时钟脉冲后,由ARICTL的控制,乘法运算过程自动中止。ARIEND输出高电平,以此可点亮一发光管,以示乘法结束。此时REG16B的输出值即为最后乘积。

四、实验步骤

2、

对最后的顶层文件进行编译、仿真和下载;

五、实验报告

1、写出实验源程序,并附上综合结果和仿真波形;

2、进行硬件逻辑验证;

3、完成实验思考题。